| Inputs | in[16] |

|---|---|

| Outputs | out[16] |

| SOP | !in[i] |

Or8Way

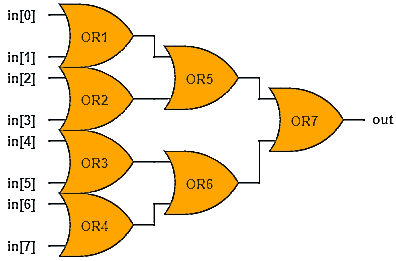

| Inputs | in[8] |

|---|---|

| Outputs | out |

| SOP | in[0]+in[1]+..+in[7] |

This document details API, schematic design, and HDL implementation for the nand2tetris course (based on "The Elements of Computing Systems"). All HDL implementations have been tested through the Hardware Simulator. (this project is hosted on Github)

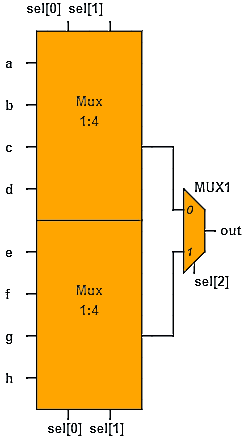

Note: schematics, truth tables, and HDL are only included where appropriate.| Inputs | a, b, c, d, e, f, g, h, sel[3] |

|---|---|

| Outputs | out |

| sel[0] | sel[1] | sel[2] | out |

|---|---|---|---|

| 0 | 0 | 0 | a |

| 0 | 1 | 0 | b |

| 1 | 0 | 0 | c |

| 1 | 1 | 0 | d |

| 0 | 0 | 1 | e |

| 0 | 1 | 1 | f |

| 1 | 0 | 1 | g |

| 1 | 1 | 1 | h |

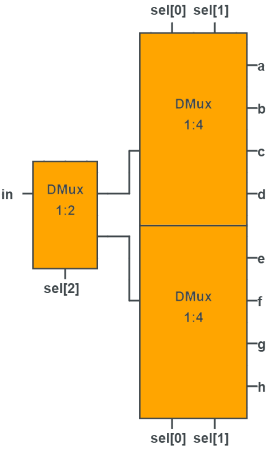

| Inputs | in, sel[2] |

|---|---|

| Outputs | a, b, c, d |

| sel[0] | sel[1] | a | b | c | d |

|---|---|---|---|---|---|

| 0 | 0 | in | 0 | 0 | 0 |

| 0 | 1 | 0 | in | 0 | 0 |

| 1 | 0 | 0 | 0 | in | 0 |

| 1 | 1 | 0 | 0 | 0 | in |

| Inputs | in, sel[3] |

|---|---|

| Outputs | a, b, c, d, e, f, g, h, out |

| sel[0] | sel[1] | sel[2] | out |

|---|---|---|---|

| 0 | 0 | 0 | a |

| 0 | 1 | 0 | b |

| 1 | 0 | 0 | c |

| 1 | 1 | 0 | d |

| 0 | 0 | 1 | e |

| 0 | 1 | 1 | f |

| 1 | 0 | 1 | g |

| 1 | 1 | 1 | h |